ADS PLL相位噪声仿真模型中计算问题

05-08

各位大神好,仿真遇到一棘手问题,希望各位大神百忙之中能够帮忙指导一下!

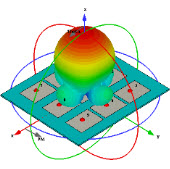

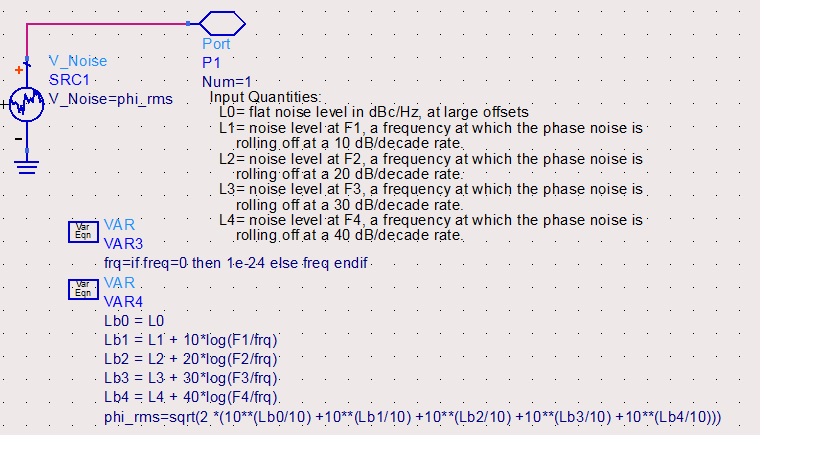

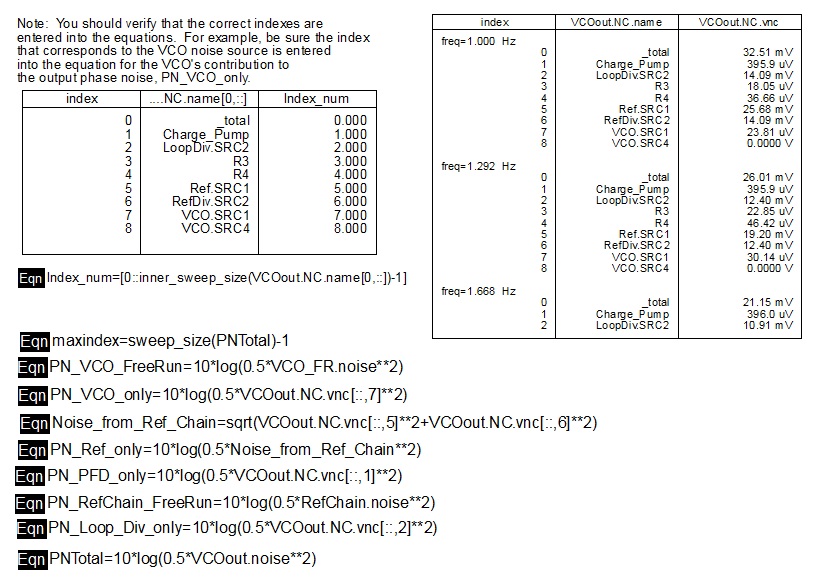

问题如下:图1的仿真模型中给定了F和L的定义,但不明白为什么L4和L3值相同?F4又为什么要设置为-1000?查了help无详细解释,相关仿真教程中也未做特别说明。还有图2和图3中的计算公式,看不太懂,那位大神清楚,能否说明一下?

在线等先谢谢大家啦!

发现什么了? 相对频率越小、-dB値就越大! 再看一次你自己的贴图...

L=-1000 按你贴图中的说明调整一下,成为40dB/-1000 -> -40dBc/1000Hz -> 十进制一下=> -40dBc / KHZ (offset)

** 由此反推当offset = 100Hz时 -30dBc/100Hz 会比-40dBc / KHZ 大,也就不足为奇了。发现第一张图的重点了吗?

这就是我说的: 形不是重点、意才能区分高下。

问题如下:图1的仿真模型中给定了F和L的定义,但不明白为什么L4和L3值相同?F4又为什么要设置为-1000?查了help无详细解释,相关仿真教程中也未做特别说明。还有图2和图3中的计算公式,看不太懂,那位大神清楚,能否说明一下?

在线等先谢谢大家啦!

第一个问题描述错了,重新阐述:对于每一个器件,为什么最后一个L和倒数第二个L的值都要为10Hz,且最后一个L对应的F=-1000?

先声明: 我只负责破题、解题是出题者的责任。

Phase Noise 的表示法是: -xx(十进位制) dBc/Hz,那个c 意思是相对。其实你要知道的亊情都在你的贴图中已经说完了!

发现什么了? 相对频率越小、-dB値就越大! 再看一次你自己的贴图...

L=-1000 按你贴图中的说明调整一下,成为40dB/-1000 -> -40dBc/1000Hz -> 十进制一下=> -40dBc / KHZ (offset)

** 由此反推当offset = 100Hz时 -30dBc/100Hz 会比-40dBc / KHZ 大,也就不足为奇了。发现第一张图的重点了吗?

这就是我说的: 形不是重点、意才能区分高下。

相关文章:

- 为何用ADS2006A作接收通道仿真时候,无法测试相位噪声啊? (05-08)

- 振荡器相位噪声pnfm (05-08)

- ADS相位噪声的仿真问题 (05-08)

- 振荡器相位噪声分析实例求解 (05-08)

- 在PLL电路中,相位噪声是与环路滤波器的带宽关系如何? (05-08)

- 如何通过ads进行有源电路的版图仿真? (05-08)

射频专业培训教程推荐