去嵌入方法测量晶体管S参数时的直流偏置问题

实验室里面没有探针平台之类的测试设备,

我想通过TRL的方法去嵌入测量表面贴装晶体管在某个直流偏置条件下的S参数,

这样子的话,必须给表面贴装的晶体管加入直流偏置,

那我如何把直流偏置带来的影响去除掉呢?

或者,是不是设计的时候可以通过注意直流偏置的隔离度,从而认为直流偏置带来的影响可以忽略不计?

还有一个问题:如果测试的晶体管不稳定(管子可能低频不稳,想要测试S参数又尽量不打算加其他可以加强稳定的器件),产生振荡了,这时候该如何解决?

你是要设计电路用还是也只是测测S参数而已

我是设计电路使用的,谢谢你的回答。

那个振荡的问题是说,我在测量晶体管的S参数的时候,没有添加其他可以增强稳定性的元件(尽量减少其他元件的影响),这时候如果振荡了,应该怎么解决?

那就是说源和负载都是50欧姆阻抗的时候就振荡了?

这种情况极其少见。如果你是测试的时候振荡,建议你检查Bias-Tee,极有可能就是Bias-Tee太烂了才导致振荡的。

Bias-Tee的秘密,就在于里面那个NB的大电感。各个厂商的Bias-Tee的性能,也主要取决于他们选用的电感。

顺便讲个故事:

我们组前面有两位很牛的师兄,做GaAs HBT,每次流片出来的器件探针台测试提参建模的时候都会振荡,根本就没办法测到稳定的数据和曲线。几乎想尽一切办法(去耦、屏蔽、镇流等等),还是无法解决。最后没办法建模,只好硬着头皮做电路,毕业走人。

两年后我又重复同样的事情,还是振荡。没想到,一个非常偶然的机会,探针台上原配的Focus的Bias-Tee被人借走了,我只好找了另外的一对Bias-Tee来用,是Agilent的,就不振荡了。好几年无法解决的问题,其原因就在这小小的Bias-Tee上。我打电话告诉两位师兄,他们都黯然伤神。我发现并解决这个问题,只是偶然,通常情况下,没有人会去怀疑仪器和设备,尤其是著名厂商的仪器和设备。这就是教训。

这个教训太惨重了,不过也不应该啊,做RF的在debug或者测试的时候真的要怀疑一切东西,除非是经过实测验证OK的,有条件的话有两套相互验证的设备仪器更好。

这个有没有继续深入研究一下为啥呢?

也许会有点结果?

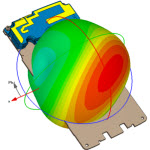

就是一种锥形线圈

.60

对,您说的没错。做RF的在Testbench上要花很多功夫,谨慎怀疑一切。尤其是测试、调试,几乎板上的每个电阻电容都会有影响。遇到过很多怪现象,比如一个主线隔直电容吃掉6dB增益,仅仅移动一个偏置网络中电容的位置1mm就可以消除振荡等等,导致现在测试的时候非常多疑,出了问题就会怀疑一切,糊里糊涂了。

前面两位师兄是做工艺出身,他们的主要精力都是在超净间,我们的GaAs工艺流程基本上就是他们做好的。到最后工艺稳定可以做电路的时候,离毕业已经挺近了。他们对于测试和电路设计不是很熟,而且那时测试专人负责,他们基本不需要自己动手。

后来到我就开始吃现成饭,工艺基本上不需要开发,主要精力就是流片,测试,提参建模,设计电路,流片,测试。那次教训之后,我们组都坚持所有流程都亲自跟着跑,这样出问题的可能会降低一些。

恩,研究过。

首先,两个Bias-Tee直接对比测试,Focus的就肯定振荡,Agilent的就不振荡;

其次,用VNA测试Bias-Tee的直通,第三端接不同的负载,发现Focus的响应会受第三端接的负载的影响比较严重,而Agilent的在它所标称的频段基本上没有影响。

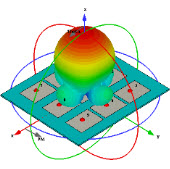

这就说明了,Focus的电感隔离不够好,直流端的负载会影响到射频端,使得器件的源和负载阻抗偏离50欧姆,恰好落到了不稳定区域,就振荡了。

未作这个验证之前,别的组的同学不同意是Bias-Tee的问题,因为他们测试别的器件就没有振荡。其实,只是这个Bias-Tee的影响,没有使他们的器件阻抗进入不稳定区域而已。所以,也和器件有关,不是所有的都会振荡。

为什么线圈要设计成锥形的呢?

有没有相关的资料或者链接? 学习一下

自己找的,共享一下

哪里说锥形线圈了,宽带的bias-tee基本上就是N多组R-L-C网络cover不同的band吧。

有个地方说到cone形的core了?

你有没有资料,分享一下? 或者说说大致的原理? RLC网络有什么讲究没?

自己绕的线圈经常容易在高端掉坑

锥形 带宽 宽

.60

这个情况时有的,如果晶体管的功率比较大,那么输入阻抗比较低,如果直接接50 Ohm的,会发生震荡的。

这位仁兄想得太乐观了,RF和DC充分隔离,实际设计时怎么个充分法,

这些都是需要很多工程经验的。

对晶体管来说,振荡一直是个主要的问题。

相关文章:

- wendk关于相对光速的测量实验方案,请大家讨论(05-08)

- 微波测量和微波测量科普书(05-08)

- 请问测量EMC有哪方面的仪器?(05-08)

- 请问有没有测量几百kHz以上交流磁场的磁感应强度的仪器?谢谢(05-08)

- 那种仪器可以测量感应场的磁场强度?谢谢!(05-08)

- 波导测量的问题(05-08)