clk对data的干扰

中间包地

没有的啊,在实际布线的时候CLK和DATA是走在一起的,紧跟在一起,并没有包底

都是差分对啊

都是差分对啊

I2C是差分信号?

能看下原理图嘛,不包地的设计真没见过。

mipi是差分走线啊,推荐小编一个文档 80-N8715-21

好的,谢谢!那我问下I2C走线的时候CLK和data之间需要包地处理吗?

额,这个我还真没注意过,特意查了一下之前的PCB,SDA和SCL两根线之间没有隔离

是的啊,我也发现clk和data之间并没有包地隔离,但是CLK不会对data产生干扰吗?

我觉得I2C这种低速线,连高通也只是要求走等长,没必要纠结时钟线和数据线之间到底有没有相互干扰吧

不必包,I2S速率低,用不着特别处理

你的意思是说I2C的CLK频率低,对DATA的干扰这块不需要特别处理,CLK线和DATA线可以紧跟在一起,不需要包地?

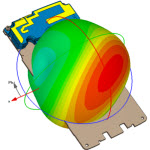

包地应该不是因为clk会干扰data,而是怕clk包地不够引起emi问题,mipi clk和data在频谱上是正好分开的。比如mipi clk 200MHz,data是0~200MHz。

学习了

mipi的CLK差分对和DATA差分对都是分别独立包地的吧,IIC的才是走在一起的,也是差分走线。

在高通平台就是直接走差分的,不需要用地分开

ps:我其实是一名技术支持

有干扰又怎么样?要评估干扰的程度是否会影响工作和性能,这种26MHz的类I2C信号,逻辑判断噪声容限早就远超板子上所能带来的程度了。

怎么会是I2C?

你说的是串扰,频率不高,没什么影响。都是数字信号

不论是clk还是data lane都是两跟线,他们的布局最好放在一层,而且走线最好相同!

都是数字信号,I2C低速还好

严格是单根包地

MIPI都是差分成对的,和CLK之间是需要包地,IIC低速信号,包地或者等长都可以不作要求

相关文章:

- QSC1110 CDMA800干扰问题(05-08)

- 射频对WiFi干扰(05-08)

- TDD频段耦合干扰问题(05-08)