solution frequency问题求助

hfss分析中的solution frequency是不是划分网格用的频率?以前看的,宽带扫描要分段扫描,不知道对不对。比如说一个滤波器,我要扫描1到12GHz,是不是先扫描1到7GHz,设置solution frequency为4GHz,然后扫描7到12GHz,solution frequency为9.5GHz?高人指点一下。感谢。着急,在线等待

嗯

HFSS仿宽带结果确实不怎么好

有可能的话建议用CST

如果只能用HFSS那就分段仿吧

过程就像小编说得那样做就行了

不过再多设置几个频点应该结果更好一些。

这样做,比不分段扫描结果应该准确吧,可以和最终的试验结果比较下

是不是更准确我也不知道,反正我看别人仿真时不分段,比如1到10GHz,直接设置solution frequency为通带中心频率,不知道有没有道理?

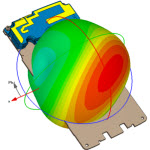

由于自适应网格划分是基于电场的,所以选择一个合适的自适应频率是很重要的。与其它的工程问题一样,任何规则都有例外。但总的来说,遵循以下的原则会帮助你正确的选择自适应频率:

1、 宽带结构

对于宽带结构来讲,由于更细的网格可以使用于所有的低频点,所以应该使用高端截止频率作为自适应频率。

2、 滤波器

对于滤波器和窄带装置而言,由于在截止频率的(阻带内)电场只在端口处出现,所以在通带或工作频率范围设置自适应频率就可。

3、 快速扫频

对于快速扫频来说,使用中心频率作为自适应频率是非常典型的。快速扫频在自适应频率点使用网格/求解。在快速扫频时如果偏离中心频率点越远,快速扫频的错误将明显增大。通常,中心频率点是用于外推求解整个频带的首选频率。对中心频率点附近的快速扫频,在中心频率点产生自适应网格是非常重要。这对于类似窄带滤波器一类的高Q值装置来说尤为重要。如果中心频率不在通带内,那么计算的带宽和谐振频率将不会准确。

4、 全波Spice输出

对于全波Spice问题而言,需使用拐点频率(Fknee≈0.5/rise_time)自适应并收敛。然后在拐点频率和最大频率之间再设置2~5个或更多频率点来自适应求解。新增频率点仅需要2-3步迭代。

1) 低于拐点频率的频率点,对时域求解影响很大。因此,拐点频率主要用于主自适应网格划分。不幸的是,如果不增加额外的自适应网格加密迭代次数,在高频端所需的网格数是肯定不够的。

2) 对于宽带较宽时,典型的方法是使用插值扫描(Interpolating Sweep)。使用多重频率扫描并合并结果的方法也是很有用的。

5、 高速数字/信号完整性

对于高速数字仿真,用户感兴趣的是宽频带范围内的性能。通过仿真才能确定频带宽度,建议采用下面的公式评估带宽:

,其中Fknee≈0.5/rise_time

总的来说,就数字信号而言,低于Fknee频率的所有频率都会有很大影响。因此一个好的高速数字设计,至少需要在不小于是Fknee的频率范围保持良好的匹配。

6、 高速数字(SPICE输出)

为了获得SPICE输出,在仿真瞬态现象时,需要很宽的带宽(≥5×Fknee)。其原因是,Fknee 是一个近似值,再加上你期望在上升时间内获得多于1个样本点。

对于全波SPICE输出,低频也是很重要。你可能期待仿真尽可能的接近直流(DC)。每个端口的设置和每个问题都因为Ansoft HFSS求解的最低频率不同而略有差异。99%的情况我们都可以仿真到100MHz。低于这个频率可能就会出错。当输出全波SPCICE时,通过从低频外推可以获得直流成分。因此从1GHz到DC,并不是精确的外推。

频率间隔。全波SPICE设置建议采用最小频率作为频率间隔。通常频率点在1000-3000个之间,这取决于扫频带宽。

7、 高速数字(自适应网格)

由于仿真带宽可能很宽,所以决定合适的自适应网格也许非常困难。建议采用如下技术:

1) 从Fknee频率自适应求解直至收敛(△S从0.02到0.01);

2) 从高于Fknee频率以上选取2~3个频率点进行自适应求解

只进行3~5次迭代,不使其收敛;

3) 求解扫描频率

如果带宽很宽,既可分割频率同时/或使用插频扫描。

8、 高速数字(技术原理)

如果低于Fknee的某个频率点对数字信号响应影响最大,应在相应频点处生成精确的网格以适应所有低于该频点以下的频率点。

如果你在很宽的频带范围仿真无源器件,其开始表现出低通滤波器的响应。所以高频成分在时域仿真中对元器件的频率响应做出的贡献很小。这就是我们不担心高频自适应收敛的原因。因此,HFSS如何进行自适应网格设置的特性也得到了充分重视。其设置是通过寻找电场中最大梯度来完成的。故如果器件表现出滤波器特征,且在滤波器的通带外进行自适应调整,我们仅重视端口处的网格设置。

现在如果你的器件在Fknee以上频率都工作的很好,那么在较高频率的自适应直到收敛都不会出现谐波。但不幸的是,对于实际问题(10-40Gb/s)的设计挑战是获得至少能达到Fknee频率的器件。

对于较宽的宽带扫描,通常使用插值扫描。该方法基于离散扫描,但它可以自适应地选取离散点并描绘曲线。插值扫频用比较少的离散点来表现宽频带特性。这些插值扫频既可以利用多项式插值,也可以利用有理函数插值。所以,这些插值方法将帮助你分割扫频范围。当频率不高于Knee频率时,宜采用多项式插值;当频率高于Knee频率时,选择有理函数插值较好。插值扫频总是会经过起始频率点和截止频率点,如果你不改变网格并且对你的每一个扫频有确定的、相匹配的起始频率点和截止频率点,则你可以把这些扫频加到一起。

9、 高速数字(设计流程)

到目前为止,关于高速数字系统的全部讨论都是基于每一个仿真都输出到SPICE的假设。一般来说,在整个设计循环中有许多进程,并不是每一个过程都需要进入SPICE。如果在Fknee频率以下存在谐振、失配、耦合等情况,在运行SPICE仿真之前,应该采用场解算器。因此,为了调查这些器件的性能,只需在1.5~2. 0 Fknee的频率范围内进行扫频。另外,对于工程设计目的而言,你也许不需要频率低于1GHz。

在这些早期的设计过程中,你也许同样希望快速扫频求解。因为,你可以获得扫描范围内每个频率点的场和S参量。这将允许你用S参量显示任何谐振响应和耦合。

另外一个用于器件封装/电路板分析的有用的工具是本征模解算器。在很多情况下,由电源和接地板平面网络所引起的谐振对设计问题的贡献最大。通过移除电源和接地板平面网络以外的所有集合结构。本征模解算器可以被用于快速识别谐振。

2、 滤波器

对于滤波器和窄带装置而言,由于在截止频率的(阻带内)电场只在端口处出现,所以在通带或工作频率范围设置自适应频率就可。

楼上意思是滤波器直接设为通带中心频率即可,确实很有道理。谢谢了!但是二次谐波(通带中心频率的2倍或其他倍数)或更高频段还是可能谐振的,很复杂

不错,顶一个。

四楼小编头两句话很强悍,不过不知道如果要仿真一个5-10G的滤波器,应该用最高截止频率还是用插值法?

是啊,同问

相关文章:

- solution type 区别 (05-08)

- 关于 solution的频率 (05-08)

- 大家教教我怎么设置Eigenmode solution (05-08)

- solution频率的设置-问题变得更大了 (05-08)

- Discrete solution, process solver died unexpectedly. (05-08)

- HFSS10仿真出现Adaptive solution, process solver : Insufficient memory (05-08)