微电子封装技术发展趋势

片式元件是应用最早、产量最大的表面组装元件。它主要有以厚薄膜工艺制造的片式电阻器和以多层厚膜共烧工艺制造的片式独石电容器,这是开发和应用最早和最广泛的片式元件。

随着工业和消费类电子产品市场对电子设备小型化、高性能、高可靠性、安全性和电磁兼容性的需求,对电子电路性能不断地提出新的要求,片式元件进一步向小型化、多层化、大容量化、耐高压、集成化和高性能化方向发展。在铝电解电容和钽电解电容片式化后,现在高Q值、耐高温、低失真的高性能MLCC已投放市场;介质厚度为10um的电容器已商品化,层数高达100层之多;出现了片式多层压敏和热敏电阻,片式多层电感器,片式多层扼流线圈,片式多层变压器和各种片式多层复合元件;在小型化方面,规格尺寸从3216→2125→1608→1005发展,目前最新出现的是0603(长0.6mm,宽0.3mm),体积缩小为原来的0.88%。 集成化是片式元件未来的另一个发展趋势,它能减少组装焊点数目和提高组装密度,集成化的元件可使Si效率(芯片面积/基板面积)达到80%以上,并能有效地提高电路性能。由于不在电路板上安装大量的分立元件,从而可极大地解决焊点失效引起的问题。

芯片封装技术:追随IC的发展而发展

数十年来,芯片封装技术一直追随着IC的发展而发展,一代IC就有相应一代的封装技术相配合,而SMT的发展,更加促进芯片封装技术不断达到新的水平。

六七十年代的中、小规模IC,曾大量使用TO型封装,后来又开发出DIP、PDIP,并成为这个时期的主导产品形式。八十年代出现了SMT,相应的IC封装形式开发出适于表面贴装短引线或无引线的LCCC、PLCC、SOP等结构。在此基础上,经十多年研制开发的QFP不但解决了LSI的封装问题,而且适于使用SMT在PCB或其他基板上表面贴装,使QFP终于成为SMT主导电子产品并延续至今。为了适应电路组装密度的进一步提高,QFP的引脚间距目前已从1.27mm发展到了0.3mm 。由于引脚间距不断缩小,I/O数不断增加,封装体积也不断加大,给电路组装生产带来了许多困难,导致成品率下降和组装成本的提高。另一方面由于受器件引脚框架加工精度等制造技术的限制0.3mm已是QFP引脚间距的极限,这都限制了组装密度的提高。于是一种先进的芯片封装BGA(Ball Grid Array)应运而生,BGA是球栅阵列的英文缩写,它的I/O端子以圆形或柱状焊点按阵列形式分布在封装下面,引线间距大,引线长度短。BGA技术的优点是可增加I/O数和间距,消除QFP技术的高I/O数带来的生产成本和可靠性问题。

BGA的兴起和发展尽管解决了QFP面临的困难,但它仍然不能满足电子产品向更加小型、更多功能、更高可靠性对电路组件的要求,也不能满足硅集成技术发展对进一步提高封装效率和进一步接近芯片本征传输速率的要求,所以更新的封装CSP(Chip Size Package)又出现了,它的英文含义是封装尺寸与裸芯片相同或封装尺寸比裸芯片稍大。日本电子工业协会对CSP规定是芯片面积与封装尺寸面积之比大于80%。CSP与BGA结构基本一样,只是锡球直径和球中心距缩小了、更薄了,这样在相同封装尺寸时可有更多的I/O数,使组装密度进一步提高,可以说CSP是缩小了的BGA。

CSP之所以受到极大关注,是由于它提供了比BGA更高的组装密度,而比采用倒装片的板极组装密度低。但是它的组装工艺却不像倒装片那么复杂,没有倒装片的裸芯片处理问题,基本上与SMT的组装工艺相一致,并且可以像SMT那样进行预测和返工。正是由于这些无法比拟的优点,才使CSP得以迅速发展并进入实用化阶段。目前日本有多家公司生产CSP,而且正越来越多地应用于移动电话、数码录像机、笔记本电脑等产品上。 从CSP近几年的发展趋势来看,CSP将取代QFP成为高I/O端子IC封装的主流。

为了最终接近IC本征传输速度,满足更高密度、更高功能和高可靠性的电路组装的要求,还必须发展裸芯片(Bare chip)技术。

从1997年以来裸芯片的年增长率已达到30%之多,发展较为迅速的裸芯片应用包括计算机的相关部件,如微处理器、高速内存和硬盘驱动器等。除此之外,一些便携式设备,如电话机和传呼机,也可望于近期大量使用这一先进的半导体封装技术。最终所有的消费电子产品由于对高性能的要求和小型化的发展趋势,也将大量使用裸芯片技术。表2是引脚数都为160的QFP、CSP、 Bare chip在外形、尺寸上的比较。

从表中可以看出若以0.65mmQFP(160pin)面积为1,则同样引脚CSP,其占用面积为0.17,而采用Bare chip其占用面积仅为0.12。元器件的缩小则可以大大推进电子产品体积的缩小,以移动电话为例,90年代重220g,而现在最轻的已达57克,可以很容易地放进上衣口袋里。

微组装:新一代组装技术

微组装技术是90年代以来在半导体集成电路技术、混合集成电路技术和表面组装技术(SMT)的基础上发展起来的新一代电子组装技术。

微组装技术是在高密度多层互连基板上,采用微焊接和封装工艺组装各种微型化片式元器件和半导体集成电路芯片,形成高密度、高速度、高可靠的三维立体机构的高级微电子组件的技术。

多芯片组件(MCM)就是当前微组装技术的代表产品。它将多个集成电路芯片和其他片式元器件组装在一块高密度多层互连基板上,然后封装在外壳内,是电路组件功能实现系统级的基础。MCM采用DCA(裸芯片直接安装技术)或CSP,使电路图形线宽达到几微米到几十微米的等级。在MCM的基础上设计与外部电路连接的扁平引线,间距为0.5mm,把几块MCM借助SMT组装在普通的PCB上就实现了系统或系统的功能。

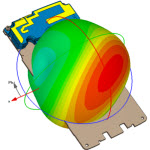

当前MCM已发展到叠装的三维电子封装(3D),即在二维X、Y平面电子封装(2D)MCM基础上,向Z方向,即空间发展的高密度电子封装技术,实现3D,不但使电子产品密度更高,也使其功能更多,传输速度更快,性能更好,可靠性更好,而电子系统相对成本却更低。

对MCM发展影响最大的莫过于IC芯片。因为MCM高成品率要求各类IC芯片都是良好的芯片(KGD),而裸芯片无论是生产厂家还是使用者都难以全面测试老化筛选,给组装MCM带来了不确定因素。

CSP的出现解决了KGD问题,CSP不但具有裸芯片的优点,还可像普通芯片一样进行测试老化筛选,使MCM的成品率才有保证,大大促进了MCM的发展和推广应用。

目前MCM已经成功地用于大型通用计算机和超级巨型机中,今后将用于工作站、个人计算机、医用电子设备和汽车电子设备等领域。

裸芯片技术主要形式

裸芯片技术有两种主要形式:一种是COB技术,另一种是倒装片技术(Flip chip) 。

COB技术

用COB技术封装的裸芯片是芯片主体和I/O端子在晶体上方,在焊接时将此裸芯片用导电/导热胶粘接在PCB上,凝固后,用 Bonder 机将金属丝(Al或Au)在超声、热压的作用下,分别连接在芯片的I/O端子焊区和PCB相对应的焊盘上,测试合格后,再封上树脂胶。 与其它封装技术相比,COB技术有以下优点:价格低廉;节约空间;工艺成熟。COB技术也存在不足,即需要另配焊接机及封装机,有时速度跟不上;PCB贴片对环境要求更为严格;无法维修等。

Flip chip 技术

Flip chip,又称为倒装片,与COB相比,芯片结构和I/O端(锡球)方向朝下,由于I/O引出端分布于整个芯片表面,故在封装密度和处理速度上Flip chip已达到顶峰,特别是它可以采用类似SMT技术的手段来加工,故是芯片封装技术及高密度安装的最终方向。90年代,该技术已在多种行业的电子产品中加以推广,特别是用于便携式的通信设备中。

裸芯片技术是当今最先进的微电子封装技术。随着电子产品体积的进一步缩小,裸芯片的应用将会越来越广泛。

大家顶起哈! 微波工艺很重要

顶一个!

:21bb:27bb:21bbc 顶

国内就是工艺比较落后

最近忙了! 好久都没灌水了! 国内现在也慢慢好起来了

相关文章:

- IC封装术语解析(05-08)

- protel元件封装总结(05-08)

- 0402封装二极管用于单端混频器的型号?(05-08)

- LTCC基板与封装的一体化制造(05-08)

- 请教各位——用那个软件设计封装?(05-08)

- 用于GHz芯片级封装的高密度插座(05-08)