|

微波射频仿真设计 |

|

|

微波射频仿真设计 |

|

| 首页 >> Ansoft Designer >> Ansoft Designer在线帮助文档 |

|

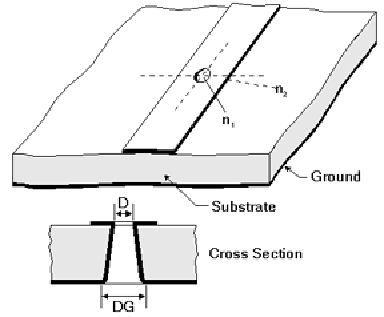

System Simulator > MS Via (MSVIAH, MSVIAH_Ref)

Notes1. To get accurate results, the following condition

should be satisfied: H << l, where: 2. If metallization is not specified (in the corresponding .SUB statement,) the VIA element behaves as an inductance only. 3. Radiation loss is included if the cover height is not defined in the .SUB statement. Netlist FormMSVIAH:NAME n1 [ n2 ] D=val [DG=val] SUB=label Netlist ExampleMSVIAH:VIA1 1 D=3.5MIL SUB=SUB1 where sub1 needs to be defined in the corresponding .sub statement. References1. Unpublished equations developed by Ansoft LLC. HFSS视频教程 ADS视频教程 CST视频教程 Ansoft Designer 中文教程 |

|

Copyright © 2006 - 2013 微波EDA网, All Rights Reserved 业务联系:mweda@163.com |

|