|

微波射频仿真设计 |

|

|

微波射频仿真设计 |

|

| 首页 >> Ansoft Designer >> Ansoft Designer在线帮助文档 |

|

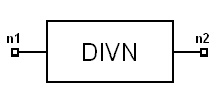

System Simulator > Divide by N Counter (DIVN)

Notes1. This element is a model of a positive edge-triggered,

modulo N down counter. The input to the element is a clock signal and

the output is a signal that is high or low, depending on whether the

current counter value is greater or less than floor (N/2). Note that

the counter value itself is not available as an output. M(0) = N0 M(k) = (M(k-1) -1) modulo N, k ³ 1

2. The initial counter value N0 is limited to the range [0, N-1] where N is the divide-by factor. 3. The input and output signal voltages of the DIVN element, with parameters N=7 and N0=1, are shown. Output is low until the first positive clock edge occurs at time 10 msec. Output jumps to high level at 10 msec, since initial counter N0=1 (< floor (7/2) ). 4. Note that the period of the input signal is 10msec and the period of the output period is 70msec, which yields the signal frequency divided

by 7 after the element.

Netlist FormDIVN:Name n1 n2 [Rin1=Val] [Rout=Val] Netlist ExampleDIVN:1 1 2 HFSS视频教程 ADS视频教程 CST视频教程 Ansoft Designer 中文教程 |

||||||||||||||||||||||||||||||||||||||||||

|

Copyright © 2006 - 2013 微波EDA网, All Rights Reserved 业务联系:mweda@163.com |

|