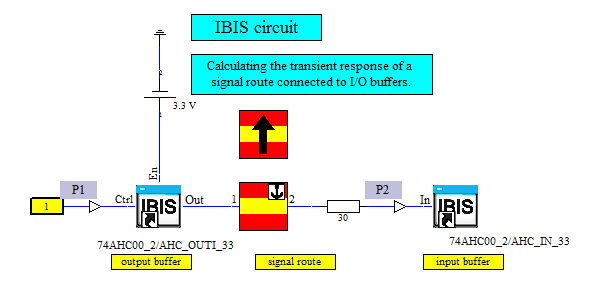

The IBIS model format was created to model the input and output buffer specifications of integrated circuits without revealing proprietary information. A transient simulation is carried out on a simple circuit, modelling a signal route between an output buffer and an input buffer.

The signal route is modelled by a 250 mm long, 40 Ω microstrip line. The input- and output buffers of a 74AHC00 quad 2-input NAND gate are represented by IBIS models. The modelling file ahc00.ibs has been provided by the manufacturer NXP. For both devices, a simplified layout has been used, i.e., internal supplies have been extracted automatically from the IBIS modelling file. A 30 Ω resistor is applied for series matching. Three probes at the input and output of the output buffer, and at the input of the input buffer have been set to monitor voltages and currents. Multiple reflections on the signal route are clearly seen from the results.